本帖最后由 正点原子 于 2021-1-25 18:22 编辑

1)实验平台:正点原子达芬奇FPGA开发板

2)购买链接:https://detail.tmall.com/item.htm?id=624335496505

3)全套实验源码+手册+视频下载地址:http://www.openedv.com/docs/boards/fpga/zdyz_dafenqi.html

4) 正点原子官方B站:https://space.bilibili.com/394620890

5)对正点原子FPGA感兴趣的同学可以加群讨论:905624739点击加入:

第二十八章高速双路AD实验

ADC(Analog to Digital Converter即模数转换器)是大多数系统中必不可少的组成部件,用于将连续的模拟信号转换成离散的数字信号,它们是连接模电电路和数字电路必不可少的桥梁。在很多场合下,ADC的转换速度甚至直接决定了整个系统的运行速度。本章我们将使用双路高速AD模块采集外部模拟信号转换成数字信号,并在ILA中查看信号波形。

本章包括以下几个部分:

2828.1简介

28.2实验任务

28.3硬件设计

28.4程序设计

28.5下载验证

28.1简介

本章我们使用的高速双路AD模块是正点原子推出的一款高速双路模数转换模块(ATK_DUAL_HS_AD),高速AD转换芯片由恩瑞浦公司生产的,型号是3PA1030。

ATK_DUAL_HS_AD模块的硬件结构图如下图所示。

图 28.1.1 ATK_DUAL_HS_AD模块硬件结构图

3PA1030芯片的输入模拟电压转换范围是0V~2V,所以电压输入端需要先经过电压衰减电路,使输入的-5V~+5V之间的电压衰减到0V~2V之间,然后经过3PA1030芯片将模拟电压信号转换成数字信号。

下面我们介绍下这个芯片。

3PA1030芯片

3PA1030是一款恩瑞浦推出的单电压芯片,10位,50 MSPS(Million Samples Per Second,每秒采样百万次)模数转换器,集成片上采样保持放大器和基准电压源。具有高性能低功耗的特点。

3PA1030的内部功能框图如下图所示:

图 28.1.2 3PA1030内部功能框图

3PA1030在时钟(CLK)的驱动下工作,3PA1030内置片内采样保持放大器(SHA),同时采用多级差分流水线架构,保证了50MSPS的数据转换速率下全温度范围内无失码;3PA1030内部集成了基准源,根据系统需要也可以选择外部高精度基准满足系统的要求。

3PA1030输出的数据以二进制格式表示,当输入的模拟电压超出量程时,会拉高OVR信号;当输入的模拟电压在量程范围内时,OVR信号为低电平,因此可以通过OVR信号来判断输入的模拟电压是否在测量范围内。另外3PA1030有一个OE信号,当该信号为高电平时3PA1030输出呈高阻态,低电平则可以正常输出。

3PA1030的时序图如下图所示:

图 28.1.3 3PA1030时序图

上图中,S1,S2,S3分别为三个采样点,可以看到,芯片在时钟的上升沿采样。需要注意的是,3PA1030芯片的最大转换速度是50MSPS,即输入的时钟最大频率为50MHz。

3PA1030支持输入的模拟电压范围是0V至2V,0V对应输出的数字信号为0,2V对应输出的数字信号为1023。而DA经外部电路后,输出的电压范围是-5V~+5V,因此在3PA1030的模拟输入端增加电压衰减电路,使-5V~+5V之间的电压转换成0V至2V之间。那么实际上对我们用户使用来说,当3PA1030的模拟输入接口连接-5V电压时,AD输出的数据为0;当3PA1030的模拟输入接口连接+5V电压时,AD输出的数据为1023。

当3PA1030模拟输入端接-5V至+5V之间变化的正弦波电压信号时,其转换后的数据也是成正弦波波形变化,转换波形如下图所示:

图 28.1.4 3PA1030正弦波模拟电压值(左)、数据(右)

由上图可知,输入的模拟电压范围在-5V至5V之间,按照正弦波波形变化,最终得到的数据也是按照正弦波波形变化。

28.2实验任务

本节实验任务是使用达芬奇开发板及双路AD扩展模块(ATK_DUAL_HS_AD模块)实现双路模数的转换,并在ILA中查看波形。本实验我们模拟输入源来自信号发生器,一个是正弦波,频率1Mhz,幅值9V;另一个是三角波,频率1Mhz,幅值5V。两路模拟信号分别接在双路AD模块的模拟信输入端。

28.3硬件设计

ATK_DUAL_HS_AD模块电路主要包括扩展口,AD芯片,电源电路模块和低通滤波器,衰减电路。下面是扩展口电源电路部分。

图 28.3.1 扩展口及电源电路

由上图可知,双路AD模块使用到的管脚连接道路JP1上,这些管脚包括十位的数据,时钟以及电源等信号。U2用于将5V电压转成VCC+(2.8V)供U1使用,U1将VCC+转成了VCC-(-2.8V),±2.8V电压供双电源运放TPH2501使用。U3负责将5V电压转成VCC(3.3V)。

衰减电路原理图如下图所示。

图 28.3.2 3PA1030原理图

上下两个电路是一样的,我们以上面的电路为例。上图中输入的模拟信号IN1(V1)经过衰减电路后得到AD_IN1(VO)信号,两个模拟电压信号之间的关系是VO=VI/5+1,即当VI=5V时,VO=2V;VI=-5V时,VO=0V。

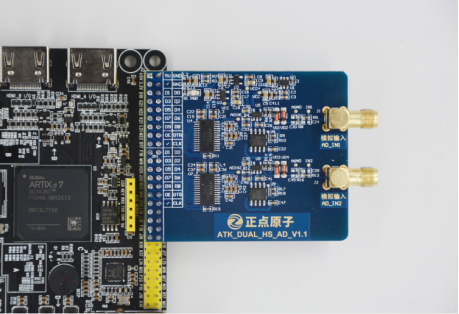

ATK_HS_AD_DA模块的实物图如下图所示。

图 28.3.3 ATK-HS-AD-DA模块实物图

本实验中,各端口信号的管脚分配如下表所示。

表 28.3.1双路高速AD转换实验管脚分配

对应的XDC约束语句如下所示:

create_clock -period 20.000 -name sys_clk [get_ports sys_clk]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN R4} [get_ports sys_clk]

#ad_data0

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN E19} [get_ports {ad0_data[0]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN G22} [get_ports {ad0_data[2]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J22} [get_ports {ad0_data[4]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN K22} [get_ports {ad0_data[6]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN M21} [get_ports {ad0_data[8]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN N22} [get_ports ad0_otr]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN E17} [get_ports ad0_clk]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN D19} [get_ports {ad0_data[1]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN G21} [get_ports {ad0_data[3]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H22} [get_ports {ad0_data[5]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN K21} [get_ports {ad0_data[7]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN L21} [get_ports {ad0_data[9]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN M22} [get_ports {ad0_oe}]

#ad_data1

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN F21} [get_ports {ad1_data[0]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN L18} [get_ports {ad1_data[2]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN G20} [get_ports {ad1_data[4]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J21} [get_ports {ad1_data[6]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN M20} [get_ports {ad1_data[8]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN N19} [get_ports ad1_otr]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN T20} [get_ports ad1_clk]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN F18} [get_ports {ad1_data[1]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN M18} [get_ports {ad1_data[3]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H20} [get_ports {ad1_data[5]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J20} [get_ports {ad1_data[7]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN N20} [get_ports {ad1_data[9]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN N18} [get_ports {ad1_oe}]

28.4程序设计

根据本章的实验任务,高速双路AD模块同时采集两路外部模拟信号,在模块内部实现模数转换,将转换后的数字信号传给FPGA管脚,FPGA内部逻辑分析仪通过抓取数据将外部的模型信号呈现出来。

图 28.4.1是根据本章实验任务画出的系统框图。我们事先准备两路模拟信号源,本实验我们使用信号发生器产生模拟输入源。接到双路AD芯片的信号输入端,在双路AD内部实现AD转换,将转换后的信号送给FPGA,在这里,FPGA只需要给AD芯片输出驱动时钟信号(AD_CLK)和使能信号(AD_OE),AD芯片便可完成模拟采集并转换成数字信号。

高速双路AD实验的系统框图如图 28.4.1所示:

图 28.4.1 双路AD系统框图

顶层模块的原理图如下图所示:

图 28.4.2 顶层模块原理图

本实验我们只用了一个模块(hs_dual_ad),用来产生AD芯片所需的驱动时钟和输出使能。同时在模块例化了一个ILA,用来观察采集到的模拟信号的波形。

模块的代码如下:

- 1 module hs_dual_ad(

- 2 input sys_clk , //系统时钟

- 3 //AD0

- 4 input [9:0] ad0_data , //AD0数据

- 5 input ad0_otr , //输入电压超过量程标志

- 6 output ad0_clk , //AD0采样时钟

- 7 output ad0_oe , //AD0输出使能

- 8 //AD1

- 9 input [9:0] ad1_data , //AD1数据

- 10 input ad1_otr , //输入电压超过量程标志

- 11 output ad1_clk , //AD1采样时钟

- 12 output ad1_oe //AD1输出使能

- 13 );

- 14

- 15 //wire define

- 16 wire clk_out1;

- 17 wire clk_out2;

- 18 //*****************************************************

- 19 //** main code

- 20 //*****************************************************

- 21 assign ad0_oe = 1'b0;

- 22 assign ad1_oe = 1'b0;

- 23 assign ad0_clk = ~clk_out1;

- 24 assign ad1_clk = ~clk_out1;

- 25

- 26 clk_wiz_0 u_clk_wiz_0

- 27 (

- 28 // Clock out ports

- 29 .clk_out1(clk_out1), // output clk_out1

- 30 // Status and control signals

- 31 .clk_out2(clk_out2), // output clk_out2

- 32 .reset(1'b0), // input reset

- 33 .locked(locked), // output locked

- 34 // Clock in ports

- 35 .clk_in1(sys_clk)); // input clk_in1

- 36

- 37 ila_0 u_ila_0 (

- 38 .clk(clk_out1), // input wire clk

- 39 .probe0(ad1_otr), // input wire [0:0] probe0

- 40 .probe1(ad0_data), // input wire [9:0] probe1

- 41 .probe2(ad0_otr), // input wire [0:0] probe0

- 42 .probe3(ad1_data) // input wire [9:0] probe1

- 43 );

- 44

- 45 endmodule

代码第21到22行产生双路AD的两个输出使能信号,ad0_oe和ad1_oe,请注意,它们是低电平有效,所以我们直接赋值0。23行到24行,产生驱动AD芯片的时钟,ad0_clk和ad1_clk,他们都是由clk_out1取反得来,取反其实就是相移180°。其中clk_out1由时钟模块产生,大小是50M。

28.5下载验证

将高速双路AD模块插入达芬奇开发板J2扩展口,连接时注意扩展口电源引脚方向和开发板电源引脚方向一致,然后将下载器一端连接电脑,另一端与开发板上对应端口连接,最后连接电源线并打开电源开关。

达芬奇开发板硬件连接实物图如下图所示:

图 28.5.1 达芬奇开发板硬件连接实物图

将工程生成的比特流文件下载到FPGA中后,

图 28.5.2 信号发生器与双路AD模块的连接图

连接后在ILA中观察ad_data数据的变化,观察到的波形如下图所示。

图 28.5.3 AD数据接收模块采集到的ILA波形图

由上图可知,输入的ad_data数据分别为三角波和正弦波,频率和幅值与信号发生器发的设定相一致,说明AD-DA实验验证成功。

另外,在这里介绍一下如何将数据设置成波形图显示。首先选中ILA波形图中的ad_data,右键选择Waveform Style,然后选择Analog即可。如果要切换成数据显示的话,同样选中ad_data,右键选择Waveform Style,然后选择Digital就可以了,如下图所示:

图 28.5.4 ILA波形显示设置界面

|