|

|

发表于 2009-10-6 21:18:24

|

显示全部楼层

发表于 2009-10-6 21:18:24

|

显示全部楼层

做得很精巧的啊——!!不错啊!!————我十年没摸 CPLD 了,,变得很陌生啊!!

请教::这个是“烧写器”————怎么里面还带有 EPM240 呢??——是学习板吗???

我有个 VHDL 综合的时候,需要 5 片 EPM 7096 组合才够容量,,不知道一片 EPM240 是否足够??——源码如下:仿真已Pass

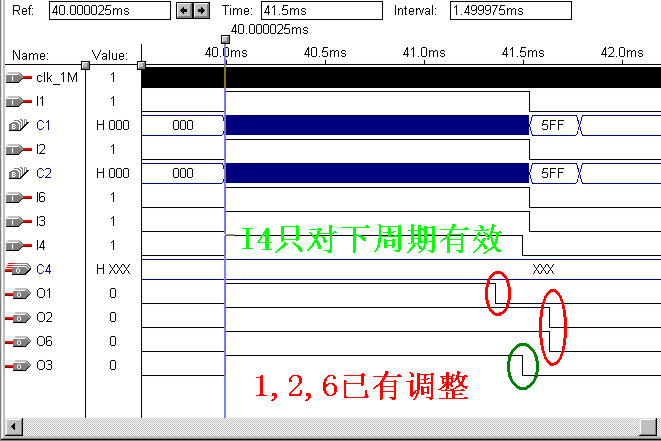

仿真已经,Pass (原文件名:共轴控制芯片.jpg)

LIBRARY IEEE;

USE IEEE.Std_Logic_1164.ALL;

USE IEEE.Std_Logic_Arith.ALL;

USE IEEE.Std_Logic_Unsigned.ALL;

entity datadelay is

port (clk_1M,I1,I2,I6,I4,I3:IN Std_Logic;

O1,O2,O6,OT4,O3:Out Std_Logic);

end datadelay;

architecture inference of datadelay is

signal Tcon:Std_Logic_Vector(14 Downto 0);

signal C1:Std_Logic_Vector(11 Downto 0);

signal C2:Std_Logic_Vector(11 Downto 0);

signal C6:Std_Logic_Vector(11 Downto 0);

signal C4:Std_Logic_Vector(11 Downto 0);

signal C3:Std_Logic_Vector(11 Downto 0);

signal T1:Std_Logic_Vector(7 Downto 0);

signal T2:Std_Logic_Vector(7 Downto 0);

signal T6:Std_Logic_Vector(7 Downto 0);

signal T4:Std_Logic_Vector(7 Downto 0);

signal T3:Std_Logic_Vector(7 Downto 0);

signal R1:Std_Logic_Vector(11 Downto 0);

signal R2:Std_Logic_Vector(11 Downto 0);

signal R6:Std_Logic_Vector(11 Downto 0);

signal R4:Std_Logic_Vector(11 Downto 0);

signal R3:Std_Logic_Vector(11 Downto 0);

signal J1:Std_Logic_Vector(11 Downto 0);

signal J2:Std_Logic_Vector(11 Downto 0);

signal J6:Std_Logic_Vector(11 Downto 0);

signal J3:Std_Logic_Vector(11 Downto 0);

signal clkT20,Twr1,Twr2,Twr6,Twr4,Twr3:Std_Logic;

begin

OT4 <= R4(4);

process (clk_1M)

begin

if (clk_1M'EVENT and clk_1M='1') then

if (Tcon = Conv_Std_Logic_Vector(19999,15)) then -- Conv 19999 to S_L_V

Tcon <= "000000000000000";

clkT20 <= '1';

else

Tcon <= Tcon + '1';

clkT20 <= '0';

end if; -- 20 mS Timer END

if (I1 = '0') then

T1 <= T1 + '1';

if (T1 = Conv_Std_Logic_Vector(252,8) and C1 >= Conv_Std_Logic_Vector(575,12)) then

Twr1 <= '1';

else

Twr1 <= '0';

end if;

if (T1 >= Conv_Std_Logic_Vector(254,8)) then

C1 <= "000000000000";

end if;

else

C1 <= C1 + '1';

T1 <= "00000000";

Twr1 <= '0';

end if; -- END Part Input 1#

if (I2 = '0') then

T2 <= T2 + '1';

if (T2 = Conv_Std_Logic_Vector(252,8) and C2 >= Conv_Std_Logic_Vector(575,12)) then

Twr2 <= '1';

else

Twr2 <= '0';

end if;

if (T2 >= Conv_Std_Logic_Vector(254,8)) then

C2 <= "000000000000";

end if;

else

C2 <= C2 + '1';

T2 <= "00000000";

Twr2 <= '0';

end if; -- END Part Input 2#

if (I6 = '0') then

T6 <= T6 + '1';

if (T6 = Conv_Std_Logic_Vector(252,8) and C6 >= Conv_Std_Logic_Vector(575,12)) then

Twr6 <= '1';

else

Twr6 <= '0';

end if;

if (T6 >= Conv_Std_Logic_Vector(254,8)) then

C6 <= "000000000000";

end if;

else

C6 <= C6 + '1';

T6 <= "00000000";

Twr6 <= '0';

end if; -- END Part Input 6#

if (I4 = '0') then

T4 <= T4 + '1';

if (T4 = Conv_Std_Logic_Vector(252,8) and C4 >= Conv_Std_Logic_Vector(575,12)) then

Twr4 <= '1';

else

Twr4 <= '0';

end if;

if (T4 >= Conv_Std_Logic_Vector(254,8)) then

C4 <= "000000000000";

end if;

else

C4 <= C4 + '1';

T4 <= "00000000";

Twr4 <= '0';

end if; -- END Part Input 4#

if (I3 = '0') then

T3 <= T3 + '1';

if (T3 = Conv_Std_Logic_Vector(252,8) and C3 >= Conv_Std_Logic_Vector(575,12)) then

Twr3 <= '1';

else

Twr3 <= '0';

end if;

if (T3 >= Conv_Std_Logic_Vector(254,8)) then

C3 <= "000000000000";

end if;

else

C3 <= C3 + '1';

T3 <= "00000000";

Twr3 <= '0';

end if; -- END Part Input 3#

end if;

end process;

process (Twr1)

begin

if (Twr1'EVENT and Twr1='1') then

R1 <= C1;

end if;

end process;

process (Twr2)

begin

if (Twr2'EVENT and Twr2='1') then

R2 <= C2;

end if;

end process;

process (Twr6)

begin

if (Twr6'EVENT and Twr6='1') then

R6 <= C6;

end if;

end process;

process (Twr4)

begin

if (Twr4'EVENT and Twr4='1') then

R4 <= C4 - Conv_Std_Logic_Vector(1500,12);

end if;

end process;

process (Twr3)

begin

if (Twr3'EVENT and Twr3='1') then

R3 <= C3;

end if;

end process;

process (clkT20,clk_1M) -- OUtput every 20 mS clock

begin

if (clkT20='1') then

J1 <= R1 + R4;

J2 <= R2 - R4;

J6 <= R6 - R4;

J3 <= R3;

elsif (clk_1M'EVENT and clk_1M='1') then

if (J1 = "000000000000") then

O1 <= '0';

else

O1 <= '1';

J1 <= J1 - '1';

end if;

if (J2 = "000000000000") then

O2 <= '0';

else

O2 <= '1';

J2 <= J2 - '1';

end if;

if (J6 = "000000000000") then

O6 <= '0';

else

O6 <= '1';

J6 <= J6 - '1';

end if;

if (J3 = "000000000000") then

O3 <= '0';

else

O3 <= '1';

J3 <= J3 - '1';

end if;

end if;

end process;

end inference ; |

|