|

|

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

entity fenpin is

port(inclk: in std_logic;

present: in std_logic_vector(3 downto 0);

outclk: buffer std_logic);

end entity fenpin;

architecture behav of fenpin is

signal clk,clk2:std_logic;

signal count:std_logic_vector(3 downto 0);

begin

clk<=inclk xor clk2;

process(clk)

begin

if(clk'event and clk='1')

then if (count="0000")

then count<=present-1;

outclk<='1';

else

count<=count-1;

outclk<='0';

end if;

end if;

end process;

process(outclk)

begin

if(outclk'event and outclk='1')

then

clk2<=not clk2;

end if;

end process;

end behav;

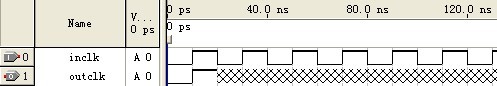

仿真结果 (原文件名:1.jpg) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

曾经有一段真挚的爱情摆在我的面前,我没有珍惜,现在想起来,还好我没有珍惜……

|