|

|

module spiflashIV(

data_ok,

clk,

addr,

mode, // 1 is write,0 is read

txdata,

rxdata,

ld_addr,//start one command

cs,

sck,

miso_temp,

mosi,

NUM

);

input[23:0] addr;

input clk;

input mode;

input[7:0] txdata;

input ld_addr; //start one bye translate

input wire miso_temp;

input[9:0] NUM;

output cs;

output sck;

output mosi;

output rxdata;

output data_ok;

reg[7:0] reset_count;

reg reset;

always@(posedge clk)

begin

reset_count<=reset_count;

if(reset_count<8'h01)begin

reset_count<=reset_count+1'b1;

reset<=1'b0;

end

else begin

reset<=1'b1;

end

end

wire miso;

assign miso=miso_temp;

reg cs;

reg data_ok;

reg[6:0] state;

reg[7:0] rxdata;

reg[7:0] rxdata_temp;

reg[1:0]STATE;

reg[9:0]num;

always@(posedge clk or negedge reset)begin

if(!reset)begin

cs<=1'b1;

state<=7'b0000000;

data_ok<=1'b0;

rxdata<=8'b00000000;

STATE<=2'b00;

num<=10'd0;

end

else begin

cs<=cs;

state<=state;

data_ok<=data_ok;

rxdata<=rxdata;

STATE<=STATE;

num<=num;

if(ld_addr)begin

cs<=1'b0;

STATE<=2'b01;

end

case(STATE)

2'b01:

begin

if(state<7'd64)begin

state<=state+1'b1;

end

else begin

STATE<=2'd2;

state<=7'd0;

end

end

2'b10:

begin

if(num<NUM)begin

if(state<7'd16)begin

state<=state+1'b1;

end

else if(state<=7'd16)begin

state<=7'd17;

data_ok<=1'b1;

rxdata<=rxdata_temp;

end

else begin

state<=7'd0;

data_ok<=1'b0;

num<=num+1'b1;

end

end

else begin

cs<=1'b1;

STATE<=2'b00;

num<=10'd0;

end

end

default:begin end

endcase

end

end

reg mosi;

reg sck;

always@(negedge clk or negedge reset)begin

if(!reset)begin

sck<=1'b0;

mosi<=1'b0;

rxdata_temp<=8'b00000000;

end

else begin

sck<=sck;

mosi<=mosi;

rxdata_temp<=rxdata_temp;

case(STATE)

2'b01:

case(state)

7'd1:begin sck<=1'b1; end

7'd2:begin sck<=1'b0; mosi<=1'b0; end

7'd3:begin sck<=1'b1; end

7'd4:begin sck<=1'b0; mosi<=1'b0; end

7'd5:begin sck<=1'b1; end

7'd6:begin sck<=1'b0; mosi<=1'b0;end

7'd7:begin sck<=1'b1; end

7'd8:begin sck<=1'b0; mosi<=1'b0;end

7'd9:begin sck<=1'b1; end

7'd10:begin sck<=1'b0; mosi<=1'b0;end

7'd11:begin sck<=1'b1; end

7'd12:begin sck<=1'b0; mosi<=1'b1;end

7'd13:begin sck<=1'b1; end

7'd14:begin sck<=1'b0; mosi<=1'b1;end

7'd15:begin sck<=1'b1; end

7'd16:begin sck<=1'b0; mosi<=addr[23];end

7'd17:begin sck<=1'b1; end

7'd18:begin sck<=1'b0; mosi<=addr[22];end

7'd19:begin sck<=1'b1; end

7'd20:begin sck<=1'b0; mosi<=addr[21];end

7'd21:begin sck<=1'b1; end

7'd22:begin sck<=1'b0; mosi<=addr[20];end

7'd23:begin sck<=1'b1; end

7'd24:begin sck<=1'b0; mosi<=addr[19]; end

7'd25:begin sck<=1'b1; end

7'd26:begin sck<=1'b0; mosi<=addr[18];end

7'd27:begin sck<=1'b1; end

7'd28:begin sck<=1'b0; mosi<=addr[17];end

7'd29:begin sck<=1'b1; end

7'd30:begin sck<=1'b0; mosi<=addr[16];end

7'd31:begin sck<=1'b1; end

7'd32:begin sck<=1'b0; mosi<=addr[15];end

7'd33:begin sck<=1'b1; end

7'd34:begin sck<=1'b0; mosi<=addr[14];end

7'd35:begin sck<=1'b1; end

7'd36:begin sck<=1'b0; mosi<=addr[13];end

7'd37:begin sck<=1'b1; end

7'd38:begin sck<=1'b0; mosi<=addr[12];end

7'd39:begin sck<=1'b1; end

7'd40:begin sck<=1'b0; mosi<=addr[11];end

7'd41:begin sck<=1'b1; end

7'd42:begin sck<=1'b0; mosi<=addr[10]; end

7'd43:begin sck<=1'b1; end

7'd44:begin sck<=1'b0; mosi<=addr[9];end

7'd45:begin sck<=1'b1; end

7'd46:begin sck<=1'b0; mosi<=addr[8];end

7'd47:begin sck<=1'b1; end

7'd48:begin sck<=1'b0; mosi<=addr[7];end

7'd49:begin sck<=1'b1; end

7'd50:begin sck<=1'b0; mosi<=addr[6];end

7'd51:begin sck<=1'b1; end

7'd52:begin sck<=1'b0; mosi<=addr[5];end

7'd53:begin sck<=1'b1; end

7'd54:begin sck<=1'b0; mosi<=addr[4];end

7'd55:begin sck<=1'b1; end

7'd56:begin sck<=1'b0; mosi<=addr[3];end

7'd57:begin sck<=1'b1; end

7'd58:begin sck<=1'b0; mosi<=addr[2];end

7'd59:begin sck<=1'b1; end

7'd60:begin sck<=1'b0; mosi<=addr[1];end

7'd61:begin sck<=1'b1; end

7'd62:begin sck<=1'b0; mosi<=addr[0];end

7'd63:begin sck<=1'b1; end

7'd64:begin sck<=1'b0; mosi<=1'b0;end

default:begin end

endcase

2'b10:

case(state)

7'd1:begin sck<=1'b1; rxdata_temp[7]<=miso;end

7'd2:begin sck<=1'b0; mosi<=1'b0; end

7'd3:begin sck<=1'b1; rxdata_temp[6]<=miso;end

7'd4:begin sck<=1'b0; mosi<=1'b0; end

7'd5:begin sck<=1'b1; rxdata_temp[5]<=miso;end

7'd6:begin sck<=1'b0; mosi<=1'b0; end

7'd7:begin sck<=1'b1; rxdata_temp[4]<=miso;end

7'd8:begin sck<=1'b0; mosi<=1'b0; end

7'd9:begin sck<=1'b1; rxdata_temp[3]<=miso;end

7'd10:begin sck<=1'b0; mosi<=1'b0; end

7'd11:begin sck<=1'b1; rxdata_temp[2]<=miso;end

7'd12:begin sck<=1'b0; mosi<=1'b0;end

7'd13:begin sck<=1'b1; rxdata_temp[1]<=miso; end

7'd14:begin sck<=1'b0; mosi<=1'b0;end

7'd15:begin sck<=1'b1; rxdata_temp[0]<=miso;end

7'd16:begin sck<=1'b0; mosi<=1'b0;end

default:begin end

endcase

default:begin end

endcase

end

end

endmodule

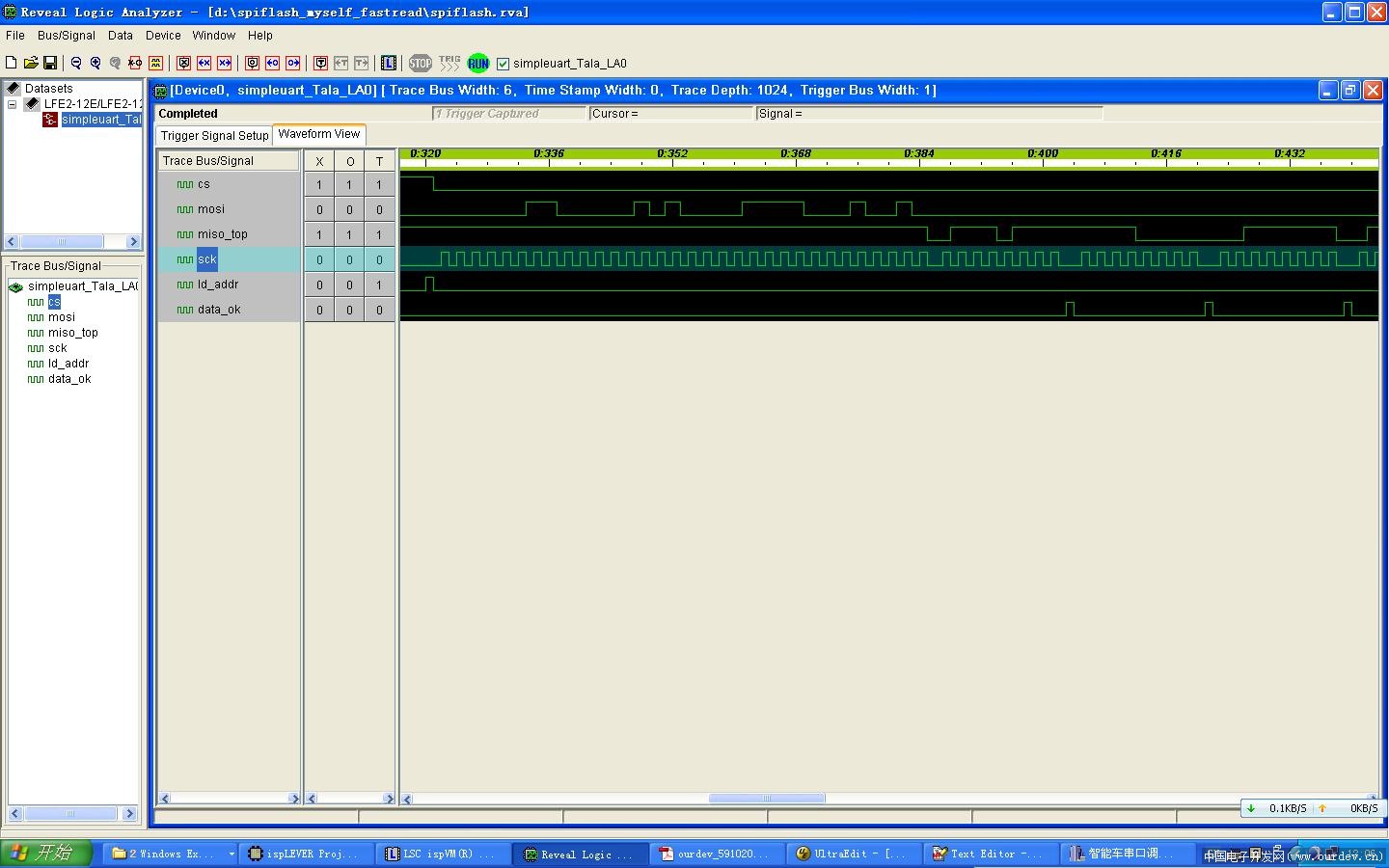

(原文件名:lattice内嵌逻辑分析仪_spiflash读时序.JPG) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

一只鸟敢站在脆弱的枝条上歇脚,它依仗的不是枝条不会断,而是自己有翅膀,会飞。

|