|

|

http://opencores.org/project,uart2bus

这是OPENCORES上为数不多经过认证的IP核之一。

在FPGA里面用上了这个核可以实现通过 UART 通讯方式 读写FPGA内部的用户自己定义的寄存器空间。

原作者对此核心的介绍如下:

Description

Have you ever needed a fast and easy way to test your new FPGA board?

You know you have all the interfaces but it will take time to finish the software or the verification just to start debugging.

This core might be what you are looking for.

The UART to Bus IP Core is a simple command parser that can be used to access an internal bus via a UART interface. The parser supports two modes of operation: text mode commands and binary mode commands. Text mode commands are designed to be used with a hyper terminal software and enable easy access to the internal bus. Binary mode commands are more efficient and also support buffered read & write operations with or without automatic address increment.

有一点补充 :此核心所能管理的地址空间是16位的,读写数据是8为的。

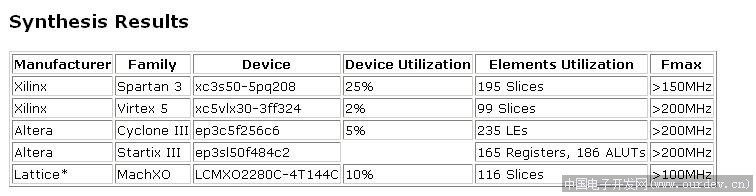

此核实际是由一个UART收发器和一个解析状态机两部分组成,占用资源很少,作者在不同的器件上综合结果列表如下:

UART2BUS核心资源占用情况 (原文件名:uart2bus_res.JPG)

这个核心是提供一种最简洁方式通过UART实现对内部FPGA内部资源的读写,所以实际使用的时候要看看UART部分 和BUS MASTER部分的协议。

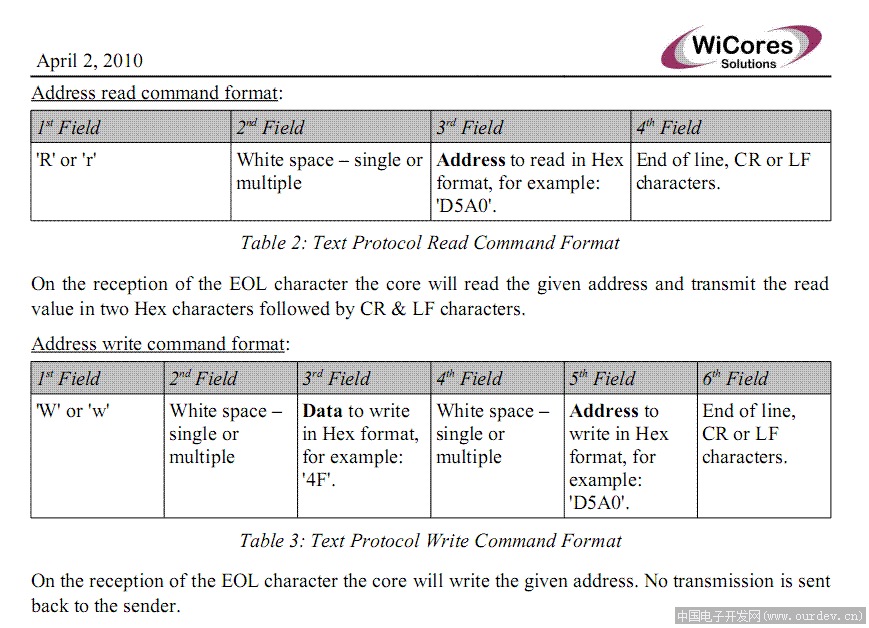

UART2BUS这个核提供了两种控制模式,二进值和文本,由于在文本模式下可以直接使用串口终端进行通讯,我觉得使用文本模式比较好。

在数据手册的第7页有下面这个图:

文本控制模式读写协议 (原文件名:u2b_asc.GIF)

这部分通讯协议是简单的:比方说要对XXXX地址写内容为YY 只需要发送 "W XXXX YY " 就可以,无返回。

要读ZZZZ 地址的 只需要发送 "R ZZZZ " 之后就会接收到返回的ASC字符的16进数值。

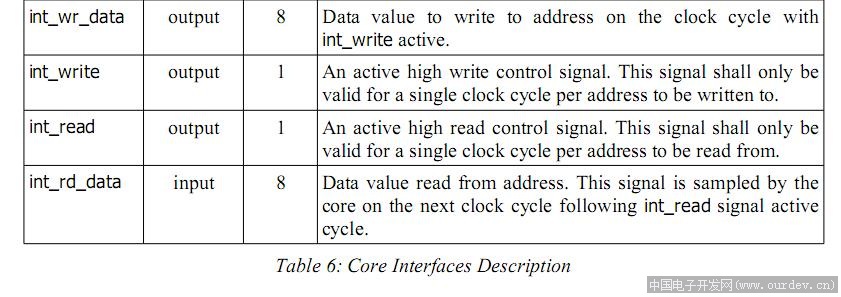

作为BUS MASTER这部分,说明书里面只是简单描述了一下:

BUS MASTER端的简单描述 (原文件名:bus_maser_if.JPG)

这个描述虽然很短,但是也很明白了,如果还是有不明白,或是不确定的地方可以看我下面所给出的例子。

另外,关于这个IP的UART部分波特率计算,作者提供了一个脚本,好像要再MATHWORK下运行,我分析了一下,核心是一个求最大公约数,用C++ BUILDER 写了一个小工具,可以直接生成波特率设置代码,生成之后COPY 到UART2BUS_TOP.V 这个文件里面替代原来的D_BAUD_FREQ 和 D_BAUD_LIMIT 这两个预定义(大约在第20行),就可以根据你板子上以及所需要的波特率进行设置。实际测试完全正确。放心使用。

生成波特率配置参数的工具ourdev_680133WNOCQK.zip(文件大小:251K) (原文件名:U2B_BAUNDRATE.zip)

比如使用主频率时钟为100M 所需要的波特率为115200 需要输入100000000 以及115200。

uart2bus 波特率计算器 (原文件名:usb_baunrate.JPG)

一下是一个例子的顶层的TOP层,是在FPGA STARTER板子上编译运行通过的。包含有读写时序。

module str_u2b_top(

input rxd,clk_i,rst,

output txd,

output [7:0] led,

output [7:0] seg7_sel,

output [7:0] seg7_data ,

input [3:0]key,

input [7:0]sw,

output reg beep

);

wire clk;

assign clk = clk_i;

PLL PLL (

.inclk0(clk_i),

.c0(clk)

);

wire [7:0] write_data;

reg [7:0] read_data;

wire write,read;

wire [15:0] addr;

reg [7:0] keyr;

reg [7:0] swr ;

always @ (posedge clk) //input

begin

swr<=sw;

keyr<={4'b0,key[3:0]};

end

uart2bus_top uart2bus_top

(

.clock(clk),

.reset(rst),

.ser_in(rxd),

.ser_out(txd),

.int_address(addr),

.int_wr_data(write_data),

.int_write(write),

.int_rd_data(read_data),

.int_read(read)

);

reg [7:0] dev_regs[15:0] ;

m_dynamic_seg7 m_dynamic_seg7(

.clk(clk),

.data0(dev_regs[0]),

.data1(dev_regs[1]),

.data2(dev_regs[2]),

.data3(dev_regs[3]),

.data4(dev_regs[4]),

.data5(dev_regs[5]),

.data6(dev_regs[6]),

.data7(dev_regs[7]),

.seg7_sel(seg7_sel),

.seg7_data(seg7_data)

);

integer i;

always @ (posedge clk)

if (rst)for(i=0;i<=15;i=i+1)dev_regs<=0;else

begin

dev_regs[8]<=swr;

dev_regs[9]<=keyr;

if (write) dev_regs[addr[3:0]]<= write_data ;

end

always @ (posedge clk)

if (read) read_data <= dev_regs[addr[3:0]];

wire [23:0] cntr_lmt = {dev_regs[13],dev_regs[12],dev_regs[11]} ;

reg [23:0] cntr ;

always@(posedge clk)

if ((cntr == cntr_lmt)||(rst==1))cntr <=0;else

cntr<=cntr+1;

always @ (posedge clk)

if (dev_regs[14]==0)beep <= 0;else

if(cntr==0)beep<=~beep;

assign led = dev_regs[10] ;

endmodule |

阿莫论坛20周年了!感谢大家的支持与爱护!!

一只鸟敢站在脆弱的枝条上歇脚,它依仗的不是枝条不会断,而是自己有翅膀,会飞。

|